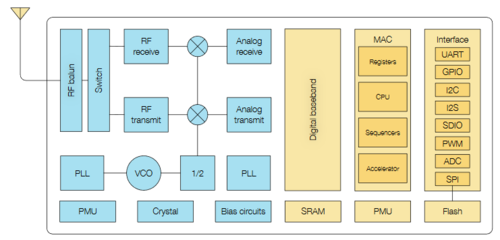

在当今高度集成的电子系统中,模拟射频(RF)集成电路(IC)扮演着至关重要的角色,广泛应用于无线通信、雷达、物联网和消费电子等领域。随着工艺尺寸的不断缩小和性能要求的日益提高,芯片的功耗密度显著增加,使得热管理成为设计中的关键挑战之一。过温保护(OTP)电路作为保障芯片可靠性和安全性的重要机制,在模拟射频IC设计中不可或缺。本文将围绕模拟射频IC中的过温保护设计进行讨论,并结合EETop等专业社区中常见的设计思路与挑战展开分析。

一、过温保护的重要性与基本原理

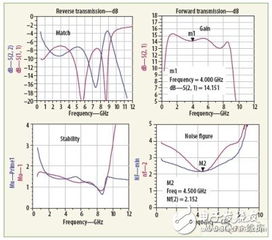

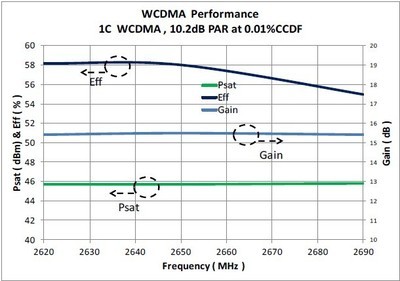

模拟射频IC,尤其是功率放大器(PA)、低噪声放大器(LNA)、混频器等模块,在工作时会产生大量热量。若芯片温度超过工艺允许的最大结温(通常为125°C至150°C),可能导致性能退化、寿命缩短甚至永久性损坏。过温保护电路通过监测芯片温度,在检测到过热时自动采取保护措施,如降低偏置电流、关闭部分电路或触发报警信号,从而防止热失控。

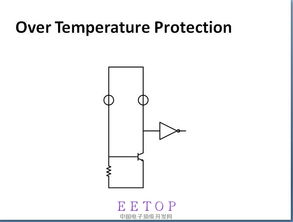

基本原理通常基于温度传感器(如带隙基准源、二极管或热敏电阻)和比较器电路。传感器将温度转换为电压信号,与预设的参考电压比较,当温度超过阈值时,输出保护信号。在射频设计中,需特别考虑保护电路的引入对高频性能(如噪声系数、线性度)的影响。

二、模拟射频IC过温保护的设计挑战

- 精度与响应速度的平衡:过温保护需要快速响应温度变化,但传感器和比较器的延迟可能影响实时性。阈值精度需控制在±5°C以内,以避免误触发或保护不足。在射频环境中,温度传感器本身可能受电磁干扰,需通过屏蔽和滤波增强鲁棒性。

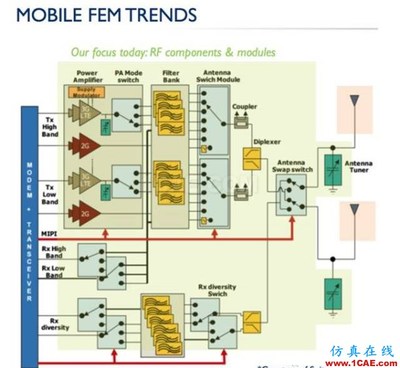

- 与射频性能的兼容性:过温保护电路通常集成在芯片的模拟或数字部分,但其布局布线需远离敏感射频路径,防止引入噪声或耦合干扰。例如,在功率放大器设计中,保护电路的电源和地线应独立隔离,避免影响输出功率和效率。

- 工艺与温度变化的影响:半导体工艺的偏差(如CMOS或GaAs工艺)会导致温度传感器特性漂移。设计时需采用工艺角分析和温度补偿技术,确保阈值在不同工艺批次和温度范围内稳定。EETop社区中常讨论的“trimming”技术(如激光修调或数字校准)可有效提升精度。

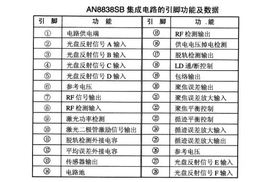

- 功耗与面积约束:过温保护电路本身应低功耗,避免加重热负荷。在面积受限的射频芯片中,需优化传感器和比较器的尺寸,例如利用现有电路(如偏置网络)复用温度传感功能。

三、设计实践与EETop社区见解

EETop作为国内最大的半导体和集成电路设计社区,汇集了大量工程师的实际经验。在模拟射频IC过温保护设计中,常见实践包括:

- 分布式温度传感:在芯片热点区域(如功率晶体管附近)放置多个传感器,实现更全面的监测,避免局部过热漏检。

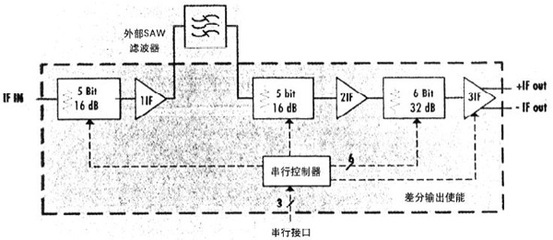

- 自适应保护策略:结合数字控制电路,根据工作模式动态调整温度阈值。例如,在高功率模式下降低阈值以提前保护,而在待机模式下提高阈值以减少误触发。

- 仿真与测试验证:利用Cadence、ADS等工具进行电热协同仿真,分析保护电路在瞬态和稳态下的行为。测试中需模拟极端环境,如高温 chamber 测试,验证保护响应的可靠性。

社区讨论还强调,过温保护不应孤立设计,而需与整体热管理方案(如封装散热、PCB布局)协同。例如,在嵌入式系统中,射频IC的过温信号可反馈至主控制器,调整系统功耗或启动风扇冷却。

四、未来趋势与

随着5G、毫米波等技术的发展,模拟射频IC将面临更高频率和更严苛的热挑战。过温保护设计正朝着智能化、集成化方向演进,例如与片上机器学习模块结合,实现预测性热管理。新材料(如氮化镓GaN)的应用也要求保护电路适配更高的温度范围。

过温保护是模拟射频IC设计中不可忽视的一环,它平衡了性能与可靠性。通过借鉴EETop等社区的经验,并持续优化设计方法,工程师可以开发出更健壮、高效的射频芯片,推动半导体行业在无线通信和嵌入式电子领域的进步。