在射频(RF)集成电路设计中,磁珠作为一种高效的噪声抑制和电磁干扰(EMI)抑制元件,其正确选用对系统性能至关重要。RF电路通常工作在高频、敏感信号环境中,不当的磁珠选择可能导致信号完整性下降、功耗增加甚至功能失效。本文将系统阐述在RF集成电路设计中,磁珠的关键选用技巧。

1. 明确应用需求与干扰频谱

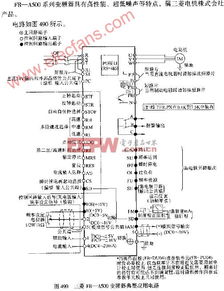

需明确磁珠的主要作用:是抑制电源线上的高频噪声,还是阻断信号线上的共模干扰?对于RF集成电路,常见的干扰源包括本振泄漏、谐波、电源纹波及数字电路开关噪声。分析干扰的中心频率与带宽是选型的第一步。例如,为抑制2.4GHz WiFi模块的谐波,需选择在该频率点附近阻抗最高的磁珠。

2. 关键参数深度解析

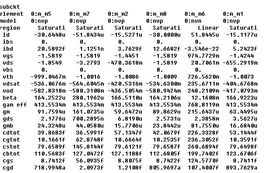

* 阻抗-频率曲线:这是磁珠的核心特性。RF设计需重点关注目标频段(如800MHz, 2.4GHz, 5.8GHz)的阻抗值。磁珠在低频时呈现感性,在高频时转化为阻性(电阻),通过耗散热能来抑制噪声。应选择在干扰频率处阻抗曲线尖锐且峰值高的型号。

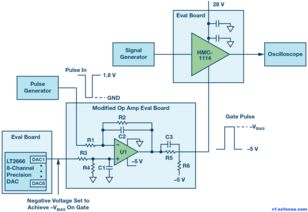

- 额定电流:必须保证磁珠的直流额定电流大于电路的最大工作电流,并留有充足裕量(通常30%-50%)。电流过载会导致磁饱和,使磁珠失效,甚至因过热而损坏。对于RF功放等大电流电路,此点尤为重要。

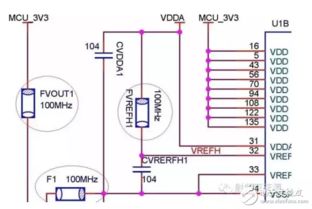

- 直流电阻(DCR):DCR会引入压降和功率损耗。在低电压、高精度的RF模拟电路(如LNA、VCO电源)中,应选择DCR极低的磁珠(如毫欧级),以避免影响电源质量和系统效率。

- 额定电压:确保其满足系统电压要求。

3. 针对RF电路的特殊考量

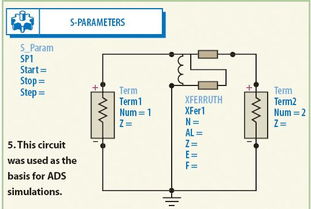

* 高频特性与寄生参数:在GHz频段,磁珠的寄生电容和引线电感会显著影响其性能。寄生电容会与磁珠的感性成分在特定频率谐振,可能产生意外的低阻抗点,让噪声通过。应选择高频模型准确、寄生参数小的贴片磁珠,并参考制造商提供的全频段S参数模型进行仿真。

- 信号完整性:若将磁珠用于高频信号线(如射频前端控制线),需评估其对信号边沿的影响。过高的阻抗可能衰减或畸变数字信号。此时可能需要选用专为信号线设计的、具有较宽平滑阻抗特性的磁珠。

- 布局与接地:磁珠必须紧靠噪声源或敏感器件放置,且其接地端需通过短而宽的走线连接到纯净的参考地平面,以确保高频噪声被有效导入地。不良的接地会严重削弱磁珠的滤波效果。

4. 选型流程与实测验证

1. 确定目标:定义要滤除的噪声频率和必须通过的信号频率。

- 初选型号:根据阻抗-频率曲线、额定电流和DCR,从知名厂商(如Murata, TDK, Taiyo Yuden)的产品库中筛选。

- 电路仿真:将磁珠的SPICE或S参数模型代入电源或信号路径中进行仿真,预评估滤波效果及对系统的影响。

- 原型测试:在实际PCB上进行测试。使用矢量网络分析仪(VNA)测量插入损耗,使用频谱分析仪验证噪声抑制效果。关注磁珠自身是否因非线性而产生新的谐波。

5. 常见误区与注意事项

* 越大越好误区:阻抗并非越高越好,需匹配干扰频点。过高的DCR和不当的频率响应反而有害。

- 忽略直流偏置影响:制造商提供的阻抗曲线通常在零偏置下测得。实际工作中,直流电流会使磁芯磁导率下降,导致高频阻抗降低。务必参考厂家提供的“阻抗-直流偏置”曲线进行修正选型。

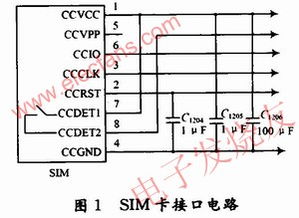

- 单一依赖磁珠:磁珠通常与旁路电容组成π型或LC型滤波网络,以达到更宽频带、更优的抑制效果。在RF电源入口处,此组合尤为常见。

****

在RF集成电路设计中,磁珠的选用是一门平衡的艺术,需在噪声抑制、信号完整性、功耗和成本之间取得最佳平衡。工程师应深入理解电路中的噪声频谱,细致比对磁珠的特性曲线,并结合仿真与实测,才能为敏感的RF电路披上高效的“抗干扰铠甲”,确保其稳定、高性能地工作。