设计一种能够在200纳秒(ns)内快速开启或关闭射频(RF)源的集成电路,是高速通信、雷达系统、脉冲射频应用等领域的关键需求。这种快速切换能力直接关系到系统的响应速度、功耗效率以及信号质量。要实现这一目标,需要从系统架构、电路拓扑、器件选择和时序控制等多个层面进行协同优化。以下是一种综合性的设计方案。

一、 系统架构与核心思路

核心思路是采用并联路径与快速偏置切换相结合的策略。传统的单一放大路径在开启和关闭时,由于偏置网络的建立与泄放需要时间(尤其是当需要稳定直流工作点时),往往难以达到纳秒级的切换速度。因此,本设计采用以下架构:

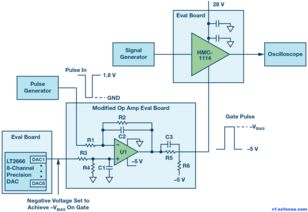

- 主射频功率路径:由核心的射频功率放大器(PA)构成,负责在“开启”状态下放大信号。

- 高速旁路/吸收路径:与主PA并联,由一个高速射频开关(如PIN二极管或GaAs FET开关)和一个终端负载(如50Ω)构成。当RF源需要“关闭”时,此路径被瞬间激活,将输入信号直接旁路到地或吸收负载,确保输出端射频能量迅速消失。

- 超高速偏置与控制电路:这是实现200 ns切换的关键。它为PA和旁路开关提供近乎瞬态变化的控制电压/电流。

二、 关键电路模块设计

- 射频功率放大器(PA)的优化:

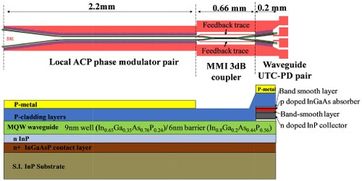

- 器件选择:选用具有高截止频率(fT)和低寄生电容的半导体工艺,例如GaAs HBT、GaN HEMT或先进的SiGe BiCMOS。这些器件本身具有更快的电荷控制能力。

- 偏置点设计:工作点设置在接近B类或深度AB类,而非纯A类。这可以降低静态电流,从而在关闭时需要移走的电荷量更少,加快关闭过程。

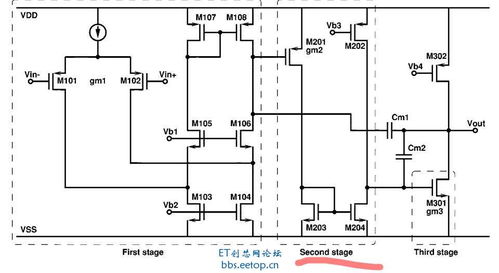

- 拓扑简化:采用级数最少的简化结构(如单级或两级),减少级间储能元件(电容、电感)的充放电时间常数。

- 高速旁路/吸收开关设计:

- 开关元件:优先选择集成PIN二极管或基于GaAs的FET开关,因其开关速度可达1-10 ns量级,远快于大多数PA的开启/关闭速度。

- 拓扑:采用串联或串并联结构,确保在“关断”状态下具有极高的隔离度(>40 dB),防止RF泄漏到输出端。

- 驱动:为该开关配备独立、极高速的TTL/CMOS兼容驱动电路,其上升/下降时间应远小于50 ns。

- 超高速偏置与控制电路(核心):

- 快速泄放路径:在PA的偏置线(如基极/栅极)上,并联一个由高速开关(如MOSFET)控制的低阻抗到地路径。当需要关闭PA时,此开关瞬间闭合,以极快的时间常数(RC小)将偏置节点上的电荷强力拉低,迫使PA立即截止。这是实现快速关闭的最有效手段。

- 高速电流源/电压源:为PA提供开启偏置的电源或电流镜,其自身也需具备快速建立能力。可采用宽带、高压摆率的运算放大器或专门设计的快速建立电流源电路。

- 时序同步:设计精密的时序控制逻辑(可由FPGA或高速逻辑电路产生),确保“关闭PA偏置”与“开启旁路开关”这两个动作在时间上高度重叠甚至略有超前,实现无缝切换。必须避免两者同时关闭的瞬间出现输出毛刺或振荡。

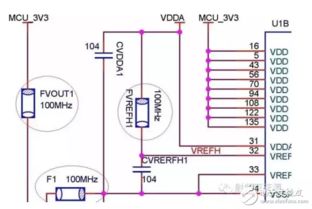

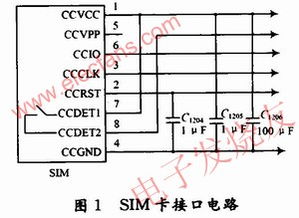

- 电源管理与去耦:

- 本地储能:在PA和驱动电路的电源引脚就近放置多层陶瓷电容(MLCC),提供瞬态大电流,确保电压稳定。

- 电源开关:对于需要极低待机功耗的应用,可使用高速MOSFET作为主电源开关,但其开关速度需纳入整体200 ns预算内。

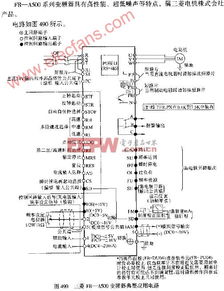

三、 实现200 ns切换的时序分析与设计要点

整个切换过程(从控制指令发出到RF输出功率达到稳定或降至足够低)的200 ns预算需要合理分配:

- 控制信号传输延迟:< 20 ns。使用匹配的高速信号线。

- 偏置控制电路响应:< 50 ns。取决于驱动器的压摆率和负载电容。

- PA本身载流子变化与输出稳定:< 100 ns。这是最耗时的部分,通过前述的快速泄放技术可以大幅缩短。

- 旁路开关动作与建立:< 30 ns。高速开关的固有优势。

- 裕量:预留约20-30 ns的时序裕量以应对工艺、电压、温度(PVT)变化。

四、 版图与封装考虑

- 最小化寄生参数:所有关键路径(尤其是偏置控制线和RF路径)必须极短,采用宽而低的电感走线,避免引入大的寄生电感和电容,这些是速度的主要杀手。

- 接地:提供极其坚固、低阻抗的接地平面,确保快速变化的电流有良好的回流路径。

- 隔离:将敏感的RF路径、高速数字控制线路和偏置电路进行良好的物理与电气隔离,防止串扰和耦合振荡。

- 封装:选择寄生电感电容小的先进封装(如QFN、晶圆级封装),或考虑系统级封装(SiP)将控制芯片与RF芯片紧耦合。

五、 验证与测试

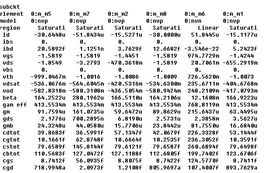

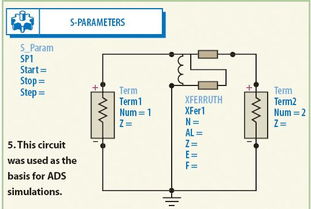

设计完成后,需通过仿真(瞬态SPICE仿真和电磁仿真结合)和实测进行验证。关键测试指标包括:

- 开启时间:从控制信号上升沿50%点到RF输出功率达到最终值90%的时间。

- 关闭时间:从控制信号下降沿50%点到RF输出功率下降至最终值10%的时间。

- 开关瞬态频谱:观察切换过程中产生的带外频谱扩展或毛刺。

- 切换期间的相位连续性(对相干系统重要)。

设计200 ns内快速切换的RF源集成电路,不能仅依赖于功率器件本身的优化,而必须构建一个包含高速旁路、主动式快速电荷泄放、精密时序同步的协同系统。通过精心设计每个子模块的速度并严格控制寄生参数,这一严苛的时序目标是完全可以实现的。