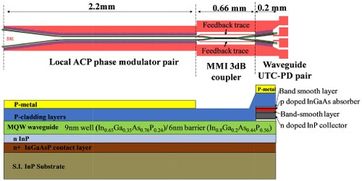

在模拟射频集成电路(Analog RF IC)设计中,两级运算放大器(运放)因其高增益、良好稳定性及设计灵活性而被广泛应用,尤其是在需要驱动较大负载或实现特定频率响应的场景中。其中,中间级电路作为连接输入级与输出级的核心枢纽,其设计优劣直接影响到整个运放乃至整个系统的性能。本文将围绕两级运放中间级电路的设计要点,结合EETOP(创芯网论坛,原名电子顶级开发网)等专业社区中常见的讨论焦点,进行深入探讨。

一、 中间级电路的核心作用与设计要求

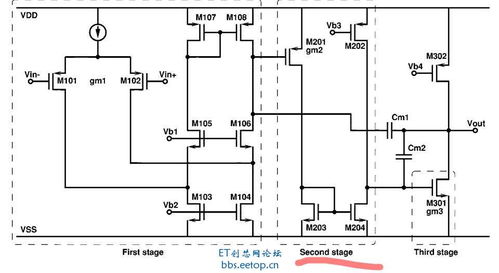

两级运放通常由输入级(差分对)、中间增益级和输出缓冲级构成。中间级的主要任务是将输入级产生的电压信号进行进一步放大,并提供足够大的摆幅以驱动输出级。在RF应用中,除了传统直流增益、带宽、功耗等指标,中间级还需特别关注:

- 频率响应与相位裕度:中间级常常引入一个主极点,是决定运放单位增益带宽和相位裕度的关键。不合理的极点分布会导致电路不稳定,产生振荡。

- 噪声性能:在射频接收链路等应用中,中间级晶体管产生的噪声会直接影响系统的噪声系数,需谨慎选择器件尺寸和偏置点。

- 线性度与摆幅:中间级需要为输出级提供足够线性且幅度合适的驱动信号,特别是在处理大信号时,其自身的线性度也至关重要。

- 隔离作用:良好的中间级应能有效隔离输入级与输出级之间的相互影响,例如防止输出级的负载变化直接反映到高增益的输入级。

二、 常见中间级电路架构及其在RF设计中的变体

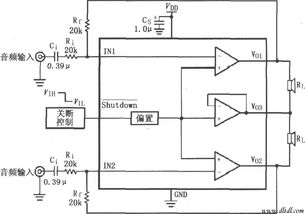

- 共源放大级(CS Stage):这是最经典、最常用的中间级结构。采用一个共源NMOS或PMOS晶体管实现高电压增益。其设计核心在于负载的选择——可以是电阻、二极管连接的MOS管(提供非线性但稳定的负载),或是电流源负载(提供高增益但摆幅受限)。在RF设计中,常会结合电感峰化(Inductive Peaking)技术来扩展带宽。

- 共源共栅级(Cascode Stage):为了增强增益、提高输出阻抗并改善频率响应(如减少米勒效应),共源共栅结构被广泛采用。折叠式共源共栅(Folded Cascode)作为输入级虽更常见,但其变体也可用于中间级,以提供更好的电源抑制比和输入输出摆幅特性。在RF领域,其优越的隔离性能备受青睐。

- 推挽式或Class-AB中间级:当需要驱动大电容负载(如下一级的栅电容)或要求高转换速率(Slew Rate)时,采用推挽结构的中间级能提供强大的电流输出能力,这对高速RF数据转换器或驱动器中的运放尤为重要。

三、 EETOP论坛热点讨论与设计权衡

浏览EETOP等工程师社区,关于此话题的讨论常围绕以下几个实际设计中的矛盾与权衡展开:

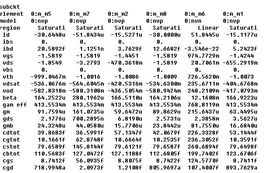

- 增益 vs. 带宽 vs. 功耗(GBW-Power Trade-off):如何在不显著增加功耗的前提下,通过优化中间级晶体管的跨导(gm)和负载,实现增益带宽积的最大化?

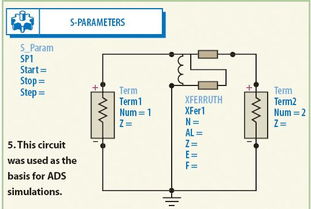

- 补偿技术:两级运放必须进行频率补偿以确保稳定性。除了传统的密勒补偿(在中间级与输出级之间跨接补偿电容),针对RF高速应用,如何运用多路径前馈零点消除、阻尼因子控制等高级补偿技术?这些是论坛中的技术精华帖常涉及的内容。

- 工艺角与PVT变化:在纳米级CMOS工艺下,工艺、电压、温度的变化对中间级偏置点和性能影响巨大。讨论常聚焦于如何设计鲁棒的偏置电路,以及使用共模反馈等技术来稳定工作点。

- 仿真与版图实践:中间级的性能极易受寄生参数影响。论坛中大量经验分享涉及如何准确进行SPICE仿真(包括稳定性、噪声、瞬态分析),以及在版图设计时如何匹配器件、减少寄生电容/电阻、进行有效的屏蔽和隔离,以确保电路实际性能与设计预期一致。

四、

两级运放的中间级远非一个简单的放大单元。在模拟RF IC的苛刻指标要求下,其设计是一个多维度的优化过程,需要在增益、带宽、噪声、线性度、功耗和稳定性之间取得精妙平衡。借鉴EETOP等平台上全球工程师的集体智慧与经验分享,深入理解经典架构的原理,并结合先进补偿技术和鲁棒性设计方法,是成功设计出适用于现代通信、雷达、传感等系统的高性能模拟射频集成电路的关键。持续关注业界讨论,实践与理论相结合,方能不断攻克中间级乃至整个运放设计的挑战。